## 0.1 - 1GHz Single Chip FM Transceiver

### FEATURES

- 100MHz to 1GHz Operating Frequency

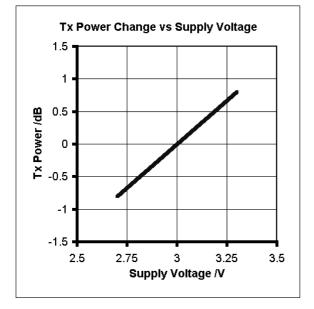

- 2.7 3.3V Operation

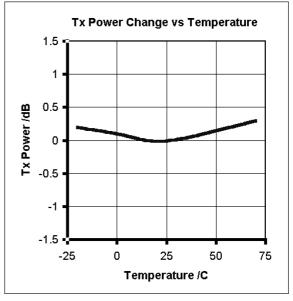

- +3.0 dBm Tx Output Power

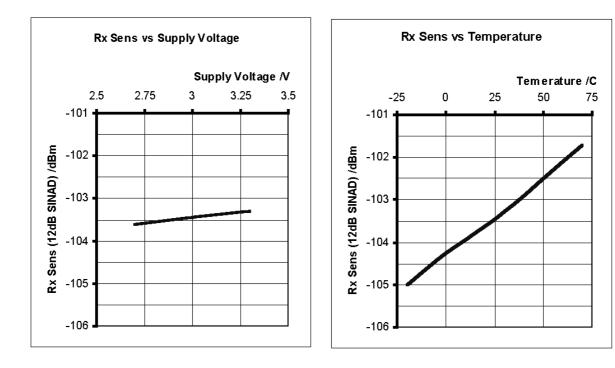

- -103 dBm Rx Sensitivity

- Full Duplex

- Dual VCO

- FM/FSK Modulator

- No Tuning "Tankless" FM Demodulator

- Direct-Conversion, Zero-IF Architecture

- Low External Component Count

- Serial Programming Interface

- Low Standby Current

- Thin-Quad Flat Package (TQFP-48)

### DESCRIPTION

WE904/905 are single-chip FM/FSK transceiver ICs operate between 100 to 1000 MHz. Utilizing a unique direct-conversion, zero-intermediate frequency (zero-IF) receiver architecture, WE904/905 provides radio designers a high performance RF transceiver solution with low external component count and small PCB footprint.

The receiver section of the WE904/905 provide all of the required receiver functions including local oscillator synthesis (VCO), down-conversion, filtering, automatic gain control (AGC), automatic frequency control (AFC), FM/FSK demodulator and RSSI functions.

The transmitter section contains a directly modulated VCO and RF power amplifier (PA).

Internal, dual, high-performance phase locked loop (PLL) synthesizers/VCOs allow full duplex or halfduplex operation over the entire RF tuning range. Tuning, power management, and gain control (manual) functions are accomplished via serial interface.

#### APPLICATIONS

- US ISM band (902-928 MHz), Europe SRD band (868MHz) Wireless Voice/Data Products

- 900 MHz Cordless Phones

- AMR/Telemetry/Data Radios

Winceiver, WE904 and WE905 are trademarks of WiNEDGE & WiRELESS Pte Ltd WE905 is recommended for new development.

0.1 - 1GHz Single Chip FM Transceiver

### TABLE OF CONTENT

| SIMPIFIED 902-9028MHZ APPLICATION CIRCUIT                                                                   | 3            |

|-------------------------------------------------------------------------------------------------------------|--------------|

| BLOCK DIAGRAM                                                                                               | 4            |

| PIN CONFIGURATION                                                                                           | 4            |

| PIN DESCRIPTIONS                                                                                            | 5            |

| FUNCTIONAL DESCRIPTION                                                                                      | 6            |

| REFERENCE OSCILLATOR                                                                                        | 9            |

| OPERATION LIMITS                                                                                            |              |

| ELECTRICAL SPECIFICATIONS                                                                                   | 10           |

| FREQUENCY OF OPERATION                                                                                      |              |

| RECEIVER BANDWIDTH ADJUSTMENT<br>BASEBAND FILTERS BANDWIDTH<br>DEMODULATOR BANDWIDTH<br>IF FILTER BANDWIDTH | . 16<br>. 17 |

| RSSI                                                                                                        |              |

| RSSI TOLERANCE                                                                                              | . 18         |

| METHODS OF CORRECTING RSSI TOLERANCE<br>RSSI SETTLING TIME                                                  |              |

| RX/TX RESPONSE TIME                                                                                         |              |

| RX/TX PLL LOCK TIME                                                                                         |              |

| RECEIVER ATTACK TIME                                                                                        |              |

| FM MODULATION                                                                                               |              |

| FM DEVIATION<br>FM MODULATOR                                                                                |              |

| AUTOMATIC FREQUENCY CONTROL (AFC)                                                                           |              |

| AFC CORRECTION RANGE                                                                                        | . 24         |

| SWITCHING AFC ON AND OFF DURING OPERATION                                                                   |              |

| CRYSTAL TUNING WITH AFC<br>WORKING CONDITIONS FOR AFC                                                       | . 25         |

| AFC NOISE                                                                                                   | . 25         |

| AFC RESPONSE TIME                                                                                           |              |

| SERIAL PROGRAMMING INTERFACE                                                                                |              |

| REFERENCE FREQUENCY REGISTER                                                                                | 27           |

| RECEIVE FREQUENCY REGISTER                                                                                  | 28           |

| TRANSMIT FREQUENCY REGISTER                                                                                 | 29           |

| MODE REGISTER                                                                                               |              |

| RX GAIN CONTROL (BIT 3, 10-15, 18-19)                                                                       | . 30         |

| AGC GAIN RESET DISABLE (BIT 15, WE905 ONLY)<br>AFC POLARITY (BIT 15, WE904 ONLY)                            |              |

| CHARGE PUMP CURRENT AND POLARITY (BIT 6-9)                                                                  | . 32         |

| ANALOG VS DIGITAL OUTPUT (BIT 17)                                                                           | . 33         |

| OPERATION MODES (BIT 18-22)<br>PROGRAMMING EXAMPLES                                                         | . 34<br>. 35 |

| CIRCUIT DESIGN CONSIDERATIONS                                                                               |              |

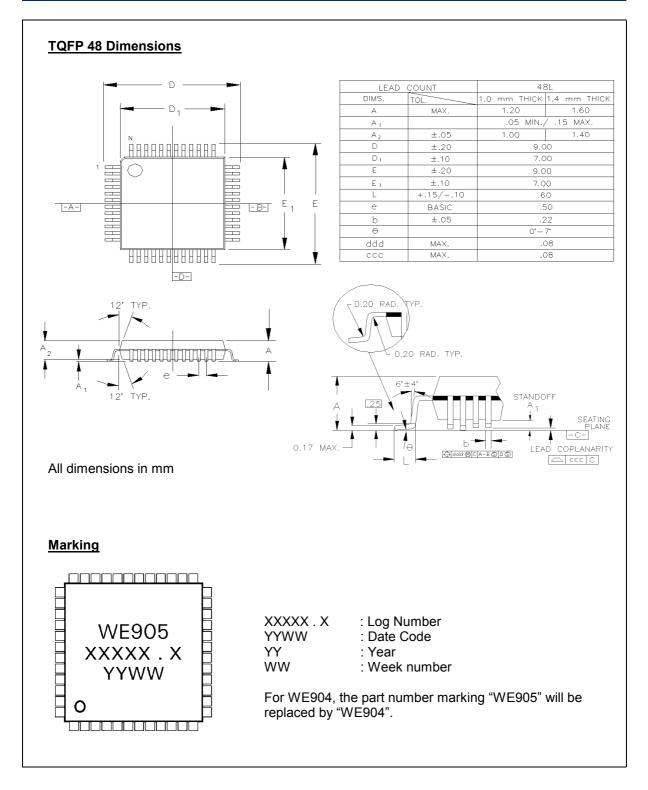

| PACKAGING INFORMATION                                                                                       |              |

| REVISION HISTORY                                                                                            |              |

| ORDERING INFORMATION                                                                                        |              |

### In this document, differences between WE904 and WE905 are highlighted in red.

0.1 - 1GHz Single Chip FM Transceiver

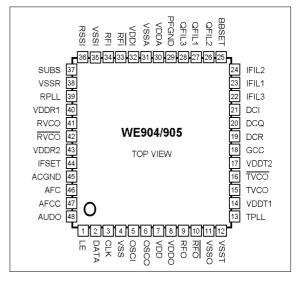

### SIMPIFIED 902-9028MHZ APPLICATION CIRCUIT

0.1 - 1GHz Single Chip FM Transceiver

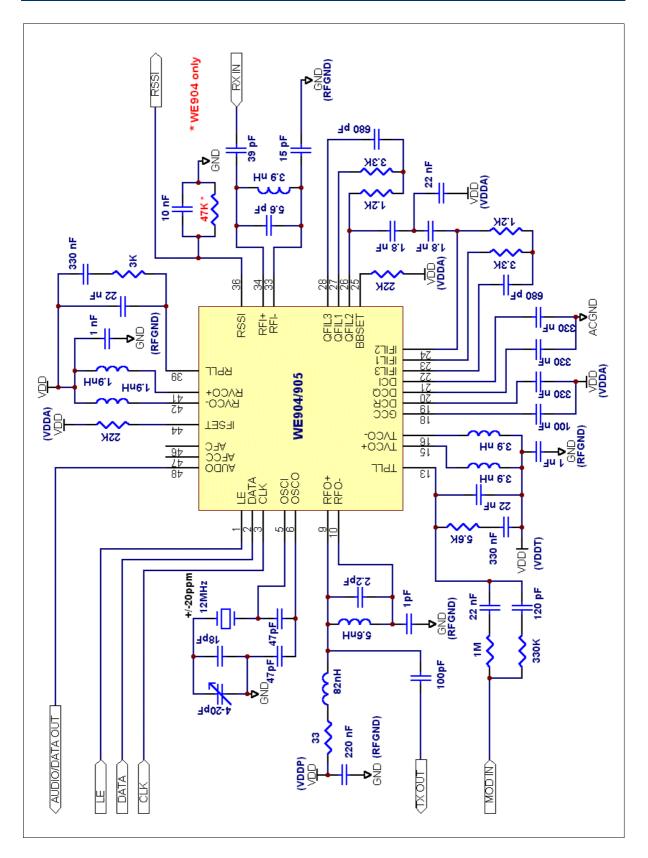

### BLOCK DIAGRAM

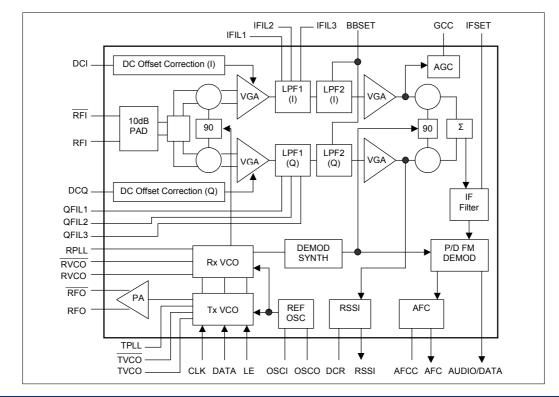

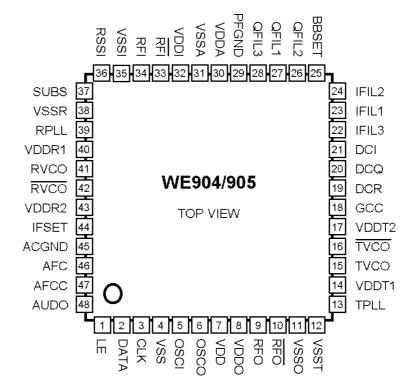

### PIN CONFIGURATION

0.1 - 1GHz Single Chip FM Transceiver

## PIN DESCRIPTIONS

| Name                | Pin        | Description                                                                                                   |  |

|---------------------|------------|---------------------------------------------------------------------------------------------------------------|--|

| LE                  | 1          | Load Enable. Active high CMOS logic compatible input                                                          |  |

| DATA                | 2          | Serial Data. CMOS logic compatible serial data input                                                          |  |

| CLK                 | 3          | Serial Clock: CMOS logic compatible, positive edge trigger input                                              |  |

| VSS                 | 4          | Digital ground. Ground pin for the internal CMOS digital circuitry                                            |  |

| OSCI                | 5          | Reference Oscillator Input. Signal level should be within the range of 200-<br>400mV peak                     |  |

| OSCO                | 6          | Reference Oscillator Output. Used in conjunction with OSCI to form a Colpitts oscillator using a crystal unit |  |

| VDD                 | 7          | Power supply for the internal CMOS digital circuitry                                                          |  |

| VDDO                | 8          | Power supply for Tx output section (PA)                                                                       |  |

| <u>RFO</u><br>RFO   | 9<br>10    | Differential Tx Outputs                                                                                       |  |

| VSSO                | 11         | Ground for Tx output section                                                                                  |  |

| VSST                | 12         | Ground for Tx VCO                                                                                             |  |

| TPLL                | 13         | Tx PLL control voltage. Connection point for PLL loop filter.                                                 |  |

| VDDT1,2             | 14, 17     | Tx power supply pins for the internal Tx VCO                                                                  |  |

| TVCO<br>TVCO        | 15<br>16   | Tx VCO Tank; establishes the natural oscillation frequency of the Tx VCO with external balanced inductors     |  |

| GCC                 | 18         | Gain control decoupling capacitor                                                                             |  |

| DCR                 | 19         | DC Offset for RSSI                                                                                            |  |

| DCI, DCQ            | 21         | DC Offset for I and Q sections of the baseband circuit                                                        |  |

| IFIL1,2,3           | 23, 24, 22 | Baseband In-phase (I) Filter                                                                                  |  |

| BBSET               | 25         | Baseband low pass filter frequency set resistor                                                               |  |

| QFIL1,2,3           | 27, 26, 28 | Baseband Quadrature (Q) Filter                                                                                |  |

| PFGND               | 29         | Internal Pre-Filter ground reference                                                                          |  |

| VDDA                | 30         | Power supply for Baseband and IF filters                                                                      |  |

| VSSA                | 31         | Ground for Baseband and IF filters                                                                            |  |

| VDDI                | 32         | Power supply for Rx Input section                                                                             |  |

| <u>RFI</u><br>RFI   | 34<br>33   | Differential Rx Inputs                                                                                        |  |

| VSSI                | 35         | Ground for Rx Input section                                                                                   |  |

| RSSI                | 36         | Receive Signal Strength Indicator output                                                                      |  |

| SUBS                | 37         | Ground to silicon substrate                                                                                   |  |

| VSSR                | 38         | Ground for Rx VCO                                                                                             |  |

| RPLL                | 39         | Rx PLL control voltage. Connection point for PLL loop filter.                                                 |  |

| VDDR1,2             | 40, 43     | Power supply for Rx VCO                                                                                       |  |

| <u>RVCO</u><br>RVCO | 41<br>42   | Rx VCO Tank:: establishes the natural oscillation frequency of the Rx VCO with external balanced inductors.   |  |

| IFSET               | 44         | IF low pass filter frequency set resistor                                                                     |  |

| ACGND               | 45         | Internal AC ground reference for the baseband and IF filters                                                  |  |

| AFC                 | 46         | Automatic Frequency Control Voltage Output                                                                    |  |

| AFCC                | 47         | Automatic Frequency Control Capacitor                                                                         |  |

| AUDO                | 48         | Rx Audio/ Digital Output                                                                                      |  |

### FUNCTIONAL DESCRIPTION

The receive section consists of several major function blocks, including a switchable RF input attenuator (PAD), quadrature down-conversion mixer, differential-to-single-ended conversion, variable gain amplifiers (VGAs), PLL synthesizer/ voltage controlled oscillator (VCO), I/Q low-pass filters, DC offset correction circuitry, quadrature up-conversion mixer, IF filter, P/D FM demodulator.

The transmit section consists of a PLL synthesizer, direct frequency modulated voltage controlled oscillator (VCO), and a RF power amplifier (PA).

Additionally, the device contains a reference crystal oscillator, an automatic frequency control (AFC) circuitry and associated reference frequency synthesizer.

A functional block diagram of the IC is shown in page 4. The following sections give details of each functional block.

### ZERO IF RECEIVER

The receiver section of the WE904/905 utilizes a quadrature mixer in a direct-conversion, zerointermediate frequency (zero-IF) approach. After quadrature down-conversion and baseband filtering, a quadrature mixer up-converts the complex baseband signal to an intermediate frequency (IF) for demodulation.

Direct conversion to zero-IF has several advantages over super-heterodyne approaches. First, the image frequency is eliminated because the IF is zero. Second, the use of active, low pass, filters provide a high level of integration, while eliminating the need for external IF filters and IF transformers.

A description of each major receive function block follows:

#### **RF Input Attenuator Pad**

A switchable 0/-10dB attenuator pad allows high signal level capability at the RF Input of the receiver. This pad is located prior to the quadrature mixer (down-conversion) and can be either manually controlled via the 3-wire interface, or automatically controlled via the AGC section of the device.

#### **Down-Conversion Quadrature Mixer**

The main advantage of the quadrature mixer is its ability to translate the RF frequency directly to a zero-IF, thereby eliminating the image frequency. Consequently, the image filter before the RF input to the WE904/905 can be eliminated. The design requirements for the duplexer and RF band pass filter may also be relaxed. In addition, the quadrature mixer achieves a lower overall noise figure by virtue of image frequency elimination.

The balanced mixers in the quadrature mixer are designed to closely track each other in both amplitude and phase response. The quadrature LO signal is generated by direct division of the receive VCO, thereby eliminating external phase shifting networks. Furthermore, for improved noise immunity, all internal RF signal paths are fully differential, thereby providing common mode noise rejection. The gain of the mixer can be adjusted via the 3-wire interface programming or automatically controlled by AGC.

### **Receive PLL Synthesizer and VCO**

The receive PLL synthesizer with voltage controlled oscillator (VCO), is designed to provide a low phase noise local oscillator. The Rx VCO operates in a balanced mode at 2x the Rx local oscillator frequency. The VCO frequency is immediately divided by a factor of 2 to provide the local oscillator for the quadrature down-conversion mixer. The synthesizer is 17 bits in total (excluding the proceeding divide by 2). These 17 bits are split into 14 bits to provide the input to the PLL phase detector to be compared with the reference frequency, with an additional 3 bits providing fractional-n capability, to allow channel frequency definition in steps of 1/8 of the PLL reference frequency.

This LO signal also drives the receive synthesizer and demodulator synthesizer.

The Rx VCO center frequency is determined by an external tank circuit comprised of an external, center-tapped, inductor. The tank circuit is connected to pin 41 and 42.

An external PLL loop filter network, connected to the RPLL pin (pin 39), filters the VCO control voltage. This control voltage is used to tune the tank frequency of the VCO via an internal, commonanode, varactor pair. The receive frequency for the WE904/905 is programmed via serial interface (Data, Clock, and Load Enable).

#### **Demodulator synthesizer**

This synthesizer consists of programmable and fixed dividers which determine the IF frequency and the demodulator bandwidth of the digital FM demodulator. The demodulator synthesizer is controlled by 3 PDR bits of the reference frequency register, programmable via serial interface. The demodulator bandwidth is programmable between 150kHz and 25kHz.

#### Variable Gain Amplifiers

The gain of the receiver can be dynamically adjusted via the serial interface to maintain signal linearity before the demodulator. This enables the achievement of high values of SINAD for an analog FM link. An Automatic Gain Control (AGC) function is also available on-chip. The gain can be adjusted in 3 locations along the receive path:

- A 10dB RF pad before the down-conversion quadrature mixer

- Four step baseband attenuators in the down-conversion quadrature mixer load circuits

- Three-step baseband Variable Gain Amplifiers after the baseband I and Q low pass filters

In addition, each VGA provides differential to single-ended conversion and amplification of the baseband signal, prior to the I/Q low-pass filters. These gain stages are referenced to pre-filter ground (PFGND), an internally generated virtual ground.

#### <u>LPF1 (I/Q)</u>

This first stage of the I/Q baseband low pass filter (LPF) section consists of active, Sallen-key type filters. These filters provide a combination of low noise figure and gain along with a wide dynamic input range. The purpose of these filters is to provide preliminary rejection of the out-of-band interferences. The reduction of out-of-band interferer levels, reduce the dynamic range requirements for the following filter stages in LPF2. The –3dB corner frequency of these LPFs are set via external RC values.

#### LPF2 (I/Q)

This second stage of the I/Q baseband low pass filter (LPF) section consists of active, transconductance (gm) type filters. Combined with LPF1, these filters provide the required channel selectivity by passing the entire desired frequency spectrum, while attenuating noise and adjacent channel interference outside of the desired signal's bandwidth.

#### DC Offset Correction

A proprietary DC offset correction circuit is used to control DC offset voltages. The use of DC offset correction improves dynamic range, minimizes LO feed-through in the up-conversion mixer, and reduces signal distortion. The correction circuit operates automatically and in a continuous mode.

#### **Up-Conversion Quadrature Mixer**

The zero-IF, complex, filtered baseband signal is translated by the quadrature up-conversion mixer to an intermidiate frequency (IF). The resultant up-converted IF signal is low enough in frequency to provide adequate SNR at the output of the period-to-digital FM demodulator, yet high enough to satisfy signal sampling criterion.

#### <u>IF BPF</u>

The band pass filter, after the quadrature up-conversion mixer, passes the IF signal and rejects the harmonic components of the up-conversion mixer's local oscillator. The IF band pass filter is comprised of cascaded, active, transconductance filters with Butterworth response characteristics. The lower corner frequency of the IF BPF is fix at 8kHz. The higher corner frequency of the filter is determined by an external resistor connected to IFSET pin.

#### <u>RSSI</u>

The receive signal strength indication (RSSI) circuitry incorporates a log amplifier and detector for the purpose of measuring the received RF carrier power level.

#### Period-to-Digital FM Demodulator

The Period-to-Digital (P/D) FM demodulator digitize the half-cycle period of the IF signal and convert that information into the demodulated FM audio signal via a digital to analog converter.

The digitizing clock signal for the P/D is derived from the Rx VCO oscillator and the P/D divide ratio (PDR). The PDR is programmable via serial interface.

### TRANSMITTER

The transmitter section of the WE904/905 is comprised of a modulation input circuit, a PLL synthesizer / VCO, and a RF power amplifier (PA) capable of providing +3.0 dBm into a  $50\Omega$  load. A description of each major function block follows:

#### Transmit PLL Synthesizer and VCO

The transmit (Tx) on-chip PLL synthesizer is identical to the receive PLL synthesizer except that it does not contain the fixed divide by 2 directly after the VCO. The transmit VCO frequency is therefore identical with the transmitter local oscillator.

The transmit PLL accepts modulation audio to provide a frequency modulated (FM) RF carrier. Utilizing a direct modulation approach, the modulation voltage is directly applied to the PLL loop filter.

The VCO center frequency is determined by an external tank circuit comprised of two inductors connected to the TVCO pins 15 and 16. An external PLL loop filter network, connected to TPLL, pin 13, filters the VCO control voltage. This control voltage ( $K_{VCO}$  26 MHz/V for 900MHz) is used to tune the tank frequency of the VCO via an internal, common-anode, varactor pair.

The transmit frequency for the WE904/905 is programmed via serial interface (Data, Clock, and Load Enable).

#### <u>PA</u>

The on-chip RF power amplifier is a differential gain stage capable of transmitting RF output power up to +4.5dBm.

The differential output impedance is ~  $700\Omega//1.2$  pF at 915MHz. In the simplified application circuit shown in page 3, a discrete LC network is used to match the output impedance to  $50\Omega$  at 915MHz ISM band. The  $33\Omega$  resistor set the output power to ~ +3dBm. A  $82\Omega$  resistor will reduce the power to -10dBm.

### **REFERENCE OSCILLATOR**

#### Crystal Oscillator and Reference Synthesizer

The reference synthesizer is comprised of an 11 bit counter which provides the PLL reference frequency for both the receiver and transmitter synthesizers. A crystal oscillator circuit normally provides the input to the reference synthesizer; however, external frequency source can be used as a reference for the synthesizer. All 11 bits of the synthesizer are fully programmable, to allow a large degree of flexibility in the choice of either the reference crystal or external reference frequency.

For WE905, this reference oscillator can be kept active when both Tx and RX are off, by programming the Mode Register, and hence, reduce turn-on time for Tx or Rx. Whereas on WE904, the reference clock will be off when both Tx and Rx are off.

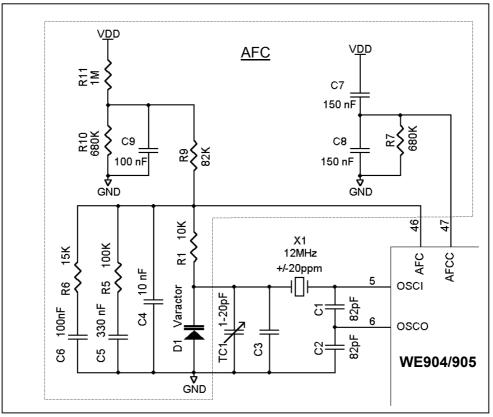

#### <u>AFC</u>

Automatic Frequency Control (AFC) of the receive local oscillator (LO) frequency is used to improve receiver performance. Without AFC, frequency offset (between receive signal and LO) causes a reduction in SINAD due to filter distortion and beat tone. The AFC minimized the offset by tuning the reference crystal oscillator. As a result, both transmit frequency and the receive LO are corrected at the same time.

The AFC correction signal is available as a DC current at the AFC output (pin 46). A varactor, connecting to the AFC output and the reference crystal, provides the required tuning action.

See section on AFC for more details.

### **OPERATION LIMITS**

| PARAMETER              | MIN | MAX  | UNITS |

|------------------------|-----|------|-------|

| Power Supply Voltage   | 2.7 | 3.3  | Vdc   |

| Operating Temperature  | -20 | 65   | С     |

| Frequency of Operation | 100 | 1000 | MHz   |

| Reference Frequency    | 5   | 20   | MHz   |

### ELECTRICAL SPECIFICATIONS

Unless otherwise specified, the specifications refer to performance of the typical 902-928MHz application circuit shown in page 3, with the following conditions.

| Supply voltages                           | = 3.0V             | Temperature                     | = 25°C              |

|-------------------------------------------|--------------------|---------------------------------|---------------------|

| Reference Oscillator                      | = 12MHz            | Reference Frequency             | = 150kHz            |

| Channel Bandwidth<br>Modulation Frequency | = 140kHz<br>= 1kHz | Channel Spacing<br>FM deviation | = 300kHz<br>= 25kHz |

| modulation requertey                      | 11012              |                                 | LONIZ               |

| PARAMETER                                             | MIN  | TYP       | MAX  | UNITS |

|-------------------------------------------------------|------|-----------|------|-------|

| DC                                                    | ·    |           |      |       |

| Supply Current (Receive Only)                         |      | 34        | 36   | mA    |

| Supply Current (Transmit Only)                        |      | 20        | 24   | mA    |

| Supply Current, Total (Rx + Tx)                       | 50   | 54        | 60   | mA    |

| Standby Current                                       |      |           | 5    | uA    |

| Receiver                                              |      |           |      |       |

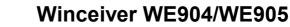

| Input Sensitivity (12dB SINAD) <sup>1</sup>           | -102 | -103      | -104 | dBm   |

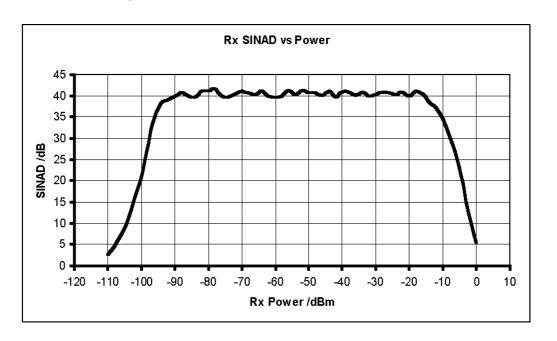

| Input Sensitivity (10 <sup>-3</sup> BER) <sup>2</sup> | -87  | -89       | -91  | dBm   |

| Input Impedance (across RFI pins)                     |      | 60Ω//0.9p |      |       |

| Maximum RF Input (12dB SINAD) <sup>1, 4</sup>         |      | -5        |      | dBm   |

| Input IP3 <sup>3</sup>                                |      | -1        |      | dBm   |

| Input 1dB Compression Point <sup>4</sup>              | -20  | -18       |      | dBm   |

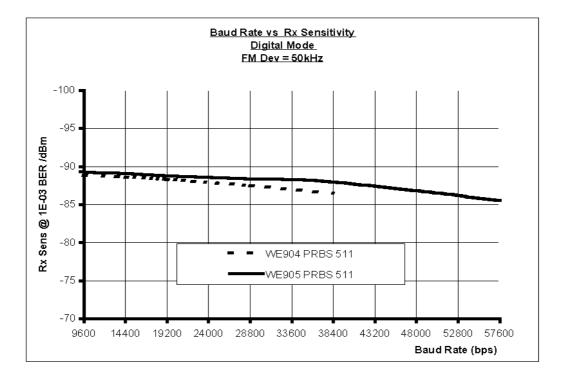

| Receiver Channel Bandwidth <sup>5</sup>               |      | 140       |      | kHz   |

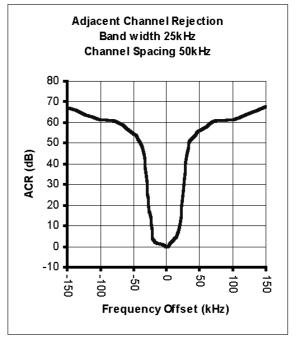

| Adjacent Channel Rejection                            | 55   | 60        | 65   | dB    |

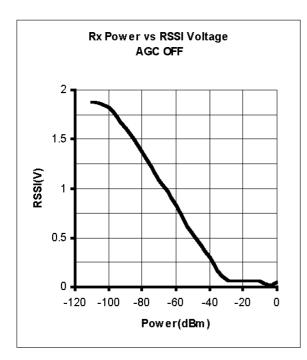

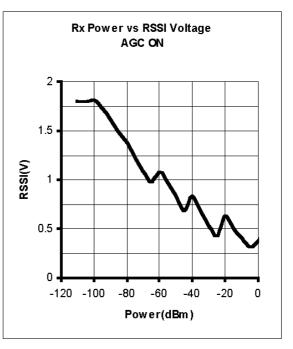

| RSSI Voltage Range (-100 to -35dBm) <sup>3</sup>      | 0.1  |           | 2.0  | Vdc   |

| RSSI Conversion Factor (Log) <sup>3</sup>             | -27  | -32       | -37  | mV/dB |

| RSSI Detection Range (Min-Max) <sup>3</sup>           | -100 |           | -35  | dBm   |

| Audio Output Level <sup>1</sup>                       | 150  | 175       | 200  | mVrms |

| Demodulation Frequency Range <sup>1</sup>             | 0.15 |           | 50   | kHz   |

| Audio Output Impedance at Pin 48                      | 2    |           | 10   | kΩ    |

| SINAD (at -85dBm) <sup>1</sup>                        | 40   | 43        |      | dB    |

| Distortion (at -85dBm) <sup>1</sup>                   |      | 0.7       | 2    | %     |

| Demodulation S/N (at -85dBm) <sup>1</sup>             | 38   | 41        |      | dB    |

| AFC Correction Range <sup>10</sup>                    |      | +/-20     |      | kHz   |

| AFC Center Frequency Tolerance                        |      | 0.5       | 2    | kHz   |

| PARAMETER                                                             | MIN | TYP          | MAX | UNITS  |

|-----------------------------------------------------------------------|-----|--------------|-----|--------|

| Transmitter                                                           | •   | •            | •   | •      |

| Transmitter Output Power <sup>6</sup>                                 | 0   | 1            | 2   | dBm    |

| Harmonic Level (2nd)                                                  |     | -50          |     | dBc    |

| Harmonic Level (3rd)                                                  |     | -40          |     | dBc    |

| Harmonic Level (4th)                                                  |     | -70          |     | dBc    |

| Modulation Input Level <sup>7</sup>                                   |     | 140          |     | mVrms  |

| Modulator Input Impedance                                             | 1   |              | 2   | kΩ     |

| Output Impedance (across RFO pins)                                    |     | 700Ω//1.2 pl | =   |        |

| Modulation S/N <sup>8</sup>                                           | 35  | 39           |     | dB     |

| Intermodulation Prod. (2*RxLO-TxLO)                                   |     | -58          |     | dBc    |

| Intermodulation Prod. (Other)                                         |     |              | -60 | dBc    |

| Phase Noise (10kHz Offset)                                            |     | -87          | -82 | dBc/Hz |

| Phase Noise (10MHz Offset)                                            |     | -150         |     | dBc/Hz |

| Response Time                                                         |     |              |     |        |

| RSSI Settling Time                                                    |     | 0.5          | 1.0 | ms     |

| Rx PLL Lock Time <sup>9</sup> : Start Up                              |     | 4            | 7   | ms     |

| Adjacent Channel                                                      |     | 2.5          | 4   | ms     |

| Audio Lag Time (from PLL locked to audio<br>appears at audio out pin) |     | 1            | 2   | ms     |

| Tx PLL Lock Time <sup>9</sup> : Start Up                              |     | 10           | 15  | ms     |

| Adjacent Channel                                                      |     | 3.5          | 5   | ms     |

<sup>1</sup> CCITT receive audio filter

<sup>2</sup> 38.4kbps 511 PRBS, Data mode

<sup>3</sup> AGC off; receiver gain maximum

<sup>4</sup> AGC on or receiver gain minimum

$\frac{5}{5}$  Bandwidth can be adjusted between 12kHz and 160kHz by external components

<sup>6</sup> Transmitter output power can be varied via an external bias resistor

<sup>7</sup> To obtain 25kHz FM deviation, input level is TPLL setting dependant

<sup>8</sup> 300Hz HPF and 3kHz LPF

<sup>9</sup> Lock time adjustable by PLL loop filters

<sup>10</sup> With varactor capacitance varies from 25pF(0.1V) to 10pF (2.5V). Refer to section on AFC

#### **Receiver Performance (Analog Mode)**

Receiver performance of 902-928MHz application circuit shown in page 3, Supply voltages · 2 01/ : 140kHz

| Supply vollages      | . 3.00 |

|----------------------|--------|

| Modulation Frequency | : 1kHz |

| AGC                  | : On   |

Channel Bandwidth FM deviation

: 25kHz (peak)

#### **Receiver Performance (Digital Mode)**

Receiver performance of 902-928MHz application circuit shown in page 3, : 140kHz Supply voltages : 3.0V **Channel Bandwidth** AFC : OFF AGC : On

0.1 - 1GHz Single Chip FM Transceiver

### FREQUENCY OF OPERATION

While the WE904/905 are well suited for use in the 902 to 928MHz ISM band, other frequencies outside of this band are also applicable. The transmitter or receiver can be used with RF frequencies from 100MHz to 1000MHz by suitable choice of external inductors or the receiver and transmitter oscillator tank circuits.

Internal, programmable trim capacitors are provided for correction of any device tolerance.

Approximate center frequency calculations are given below:

Tx VCO $f = 1/{2\pi x SQRT[(L+Lp) x Ct]}$ Rx VCO $f = 1/{2\pi x SQRT[(L+Lp) x Cr]}$ [Note Rx VCO is 2x Rx local oscillator]

Where:

L is the external inductance connected to VDDT or VDDR, from both the true and inverted tank outputs.

**Lp (= 2.6nH)** is the parasitic inductance for the TQFP or QFN 48 package.

**Ct (= 4.6pF)** is the total internal capacitance of TVCO, inclusive the TVCO varactor, internal trim capacitance at middle trim value and parasitic capacitance for the TQFP and QFN-48 package.

**Cr (= 1.7pF)** is the total internal capacitance of RVCO, inclusive the RVCO varactor, internal trim capacitance at middle trim value and parasitic capacitance for the TQFP and QFN-48 package.

The exact operating frequency is determined by programming of transmit and receive frequency registers.

Assuming a  $\pm 5\%$  tolerance on L, the guaranteed oscillator range is 3% of the center frequency if the external inductor is set for devices from the center of the distribution. Devices at the edge of the distribution can be brought to the correct center frequency by selection of the appropriate oscillator trim bit.

The Tx trim is programmed by bits 21, 22 and 23 of the transmitter frequency register; the Rx trim is programmed by bits 21 and 22 of the receiver frequency register.

### **RECEIVER BANDWIDTH ADJUSTMENT**

The application circuit diagram is given for a 915MHz ISM band receiver with a 130kHz bandwidth. The Rx bandwidths can be adjusted from 16kHz to 150kHz. Some of the bandwidth setting adjustments scale with the RF frequency. There are 3 major elements related to the receiver bandwidth:

#### Baseband Bandwidth

**BWbb**: the baseband bandwidth. This is defined by 8 pole low pass filters in both the I and Q baseband channels. The filtering in each channel is achieved by a two pole Sallen Key filter combined with a six pole Gm filter. The defining resistors and capacitors for the Sallen Key filters are off chip; the Gm filter is totally on-chip except for one bandwidth trimming resistor.

Note that the bandwidth of the individual baseband I and Q channels is half of the demodulator bandwidth. For example, a receiver working at 915MHz with a bandwidth of 130kHz (i.e.  $\pm$  65kHz), baseband bandwidth BWbb is 65kHz, demodulator bandwidth BWdm is 130kHz minimum.

The DC offset correction feedback loop in the baseband section introduces an effective high pass filter (100Hz) in the center of the RF band.

#### Demodulator Bandwidth

**BWdm**: the demodulator bandwidth. This is the bandwidth of the Period to Digital demodulator. It is a 'brick wall' filter centered on the IF frequency. BWdm must be wider than receive bandwidth.

#### IF Bandwidth

There is filtering in the IF section following the second mixer, designed to attenuate mixer products prior to the demodulator. Filtering is defined by a 4 pole low pass filter followed by a single pole high pass filter. The low pass filter is an on-chip Gm design with an off-chip bandwidth trimming resistor and the high pass filter is on-chip and fixed frequency at 8kHz.

The following sections shows how the bandwidth of these sections can be adjusted.

#### **BASEBAND FILTERS BANDWIDTH**

#### A. Sallen Key baseband filters

The R and C components for this filter are off chip. To set the baseband bandwidth, BWbb, adjust the C values. Choose values to give a bandwidth equal to or slightly greater than the required bandwidth according to the following formulae.

The recommended component tolerances for resistors should be 1%, with capacitor tolerances of 5%, or better.

#### Capacitor attached to IFIL2/QFIL2 = 1.8nF x (65kHz/BWbb) Capacitor attached to IFIL3/QFIL3 = 0.68nF x (65kHz/BWbb)

E.G., for a required 32kHz bandwidth, BWbb=16kHz, suggested values of 6.8nF and 2.6nF give a bandwidth of 34kHz.

#### B. Gm baseband filter

On-chip baseband filter bandwidth is adjusted by choice of the external resistor between VDDA and BBSET. Choose this resistor to give a same bandwidth as above.

#### $R = 22k\Omega \times (65kHz/BWbb)$

E.G., for 32kHz ( $\pm$ 16kHz) bandwidth, BWbb=16kHz, suggested value is 82k $\Omega$ .

#### C. DC Offset Correction Loop (Effective Baseband High Pass Filter)

The 3dB bandwidth is set to  $\pm 100$ Hz by the external 330nF capacitors connected to DCI and DCQ. The HP cut off can be adjusted by inverse proportional change in DCI/DCQ capacitor. For example, in digital application, if the lowest data rate is 2400bps (1.2kHz), the cut off can be increased from 100Hz to 1kHz by reducing the capacitance to 33nF.

Reduction in the cut off lower than 100Hz, with BWdm=130kHz may lead to instability in Auto Gain Control mode.

| Common  | BWbb     | IFIL2/QFIL2 | IFIL3/QFIL3 | BBSET |

|---------|----------|-------------|-------------|-------|

| Rx BW   |          | Cap /nF     | Cap /nF     | R /kΩ |

| 150 kHz | 75 kHz   | 1.5         | 0.56        | 18    |

| 130 kHz | 65 kHz   | 1.8         | 0.68        | 22    |

| 100 kHz | 50 kHz   | 2.2         | 0.82        | 27    |

| 50 kHz  | 25 kHz   | 4.7         | 1.80        | 56    |

| 25 kHz  | 12.5 kHz | 9.1         | 3.30        | 110   |

### DEMODULATOR BANDWIDTH

Demodulator bandwidth, BWdm, is adjusted by the choice of the Period to Digital demodulator clock frequency, Fpd. The chip divides down the receiver local oscillator, Frf, by the divide ratio, PDR, to obtain Fpd.

#### Fpd = Frf/PDR

PDR is programmed by bits 14, 15 & 16 of the reference frequency register.

Allowable PDR divide ratios for WE904 are  $2^1$ ,  $6^2$ , 12, 24, 36, 48, 72, and 96. Allowable PDR divide ratios for WE905 are  $3^3$ ,  $9^4$ , 12, 24, 36, 48, 72, and 96.

<sup>1</sup>Ratio 2 can only be used on WE904 with Frf < 180MHz <sup>2</sup>Ratio 6 can only be used on WE904 with Frf < 540MHz <sup>3</sup>Ratio 3 can only be used on WE905 with Frf < 277MHz <sup>4</sup>Ratio 9 can only be used on WE905 with Frf < 830MHz

The choice of Fpd directly sets the IF frequency Fif, and BWdm:

#### Fif = Fpd/544 BWdm = Fpd/580

Choose a value of PDR to give  $BWdm > 2 \times BWbb$ .

### **IF FILTER BANDWIDTH**

The bandwidth of the on-chip IF low pass filter, which precedes the Period to Digital demodulator, should be optimized as follows. Following the calculation of Fif and BWdm from section above, the filter bandwidth is adjusted by choice of the external resistor between VDDA and IFSET.

#### $R = 22k\Omega \times 206kHz / (Fif + 0.5 \times BWdm)$

There is an on-chip high pass IF filter fixed at 8kHz.

#### Examples

| Rx Freq  | PDR | Fpd /MHz | Fif /kHz | BWdm  | Suitable for | Recommended |

|----------|-----|----------|----------|-------|--------------|-------------|

| Frf /MHz |     | -        |          | /kHz  | Rx BW /kHz   | IFSET R /kΩ |

| 915      | 12  | 76.25    | 140.2    | 131.5 | 130          | 22          |

| 930      | 48  | 19.4     | 35.6     | 33.4  | 25           | 82          |

| 869      | 24  | 36.2     | 66.5     | 62.4  | 50           | 47          |

| 434      | 24  | 18.1     | 33.2     | 31.2  | 25           | 91          |

#### RSSI

For WE904, the RSSI output is a current source which work with external shunt resistor and capacitor (47k $\Omega$  || 10nF) to develop a filtered voltage level inversely proportional to the receive RF signal strength.

For WE905, the matched shunt resistor is provided internally. This eliminates the error due to tolerance of external discrete resistor. Only a 10nF capacitor is required on RSSI pin.

The RSSI measurement range is from -100dBm to -35dBm, with the RF input pad bypassed (0dB) and the quadrature mixer gain stage set to high. This range is extended as the receiver gain is reduced. The RSSI conversion factor is  $\cong$  (-30mV/dB), with a voltage range of 2.1 to 0.1 Vdc.

### **RSSI TOLERANCE**

For WE904, typically with 5%  $47k\Omega$  resistor, the RSSI voltage tolerance is about +/-10%.

For WE905, the RSSI tolerance is about +/-2%.

If external low noise amplifier (LNA) and filters are added at the Rx front end, the LNA gain and filter loss will vary from unit to unit and will contribute to additional RSSI variation above the IC's RSSI tolerance.

As the RSSI voltage depends on its load, it should be connected only to an ADC or a comparator with high input impedance.

### **METHODS OF CORRECTING RSSI TOLERANCE**

For applications that require accurate RSSI, the tolerance can be corrected by the use of an analog-to-digital converter (ADC) or a trimmer pot meter.

If ADC is used, the tolerance can be corrected using software.

If non-volatile memory (EEPROM or flash) is available, correction can be done during production testing. The ADC can read RSSI values at no signal and at a know Rx signal level, and store those values to correct for the RSSI tolerance.

If non-volatile memory (EEPROM or flash) is not available, correct can be done by checking and remember, in the RAM, the RSSI value with no Rx signal, such as when LNA is off; or when antenna switch is off at Rx side; or when Rx frequency is set to an impossible frequency.

If comparator is used, the tolerance can be corrected by adjust a trimmer pot meter.

### **RSSI SETTLING TIME**

For 130kHz Rx bandwidth, ~25kHz FM deviation, and with recommended 10nF external capacitor attached to RSSI pin, the RSSI reaches 80% of its final value in approximately 0.5ms.

If the FM signal carried is varying significantly in amplitude (e.g. FSK, switching between FM deviation limits) then a longer integration time (i.e. larger RSSI capacitor) will be required for accurate measurement of RX signal strength. Hence, settling time will be longer.

Also, for a narrower Rx bandwidth, the capacitor should be increased to integrate the received power over a longer time. The increase should be inverse proportional to the bandwidth. RSSI response time will also increase accordingly.

### **RX/TX RESPONSE TIME**

### RX/TX PLL LOCK TIME

The values shown below are based upon calculations using the component values shown in application circuit with Rx and Tx charge pump currents being 1.0mA and 0.2mA respectively; and reference frequency being 100kHz.

| <b>∆</b> Frequency      | Rx     | Тх    |

|-------------------------|--------|-------|

| From start up           | 8.5 ms | 17 ms |

| 10MHz frequency change  | 6.5 ms | 14 ms |

| 1.0MHz frequency change | 5.0 ms | 11 ms |

| 0.1MHz frequency change | 3.5 ms | 7 ms  |

Note: The settling time for Tx are based upon a 150 Hz high pass filter (HPF) cut off frequency. This filter can be adjusted via the external Tx PLL loop filter components, or by the on-chip Tx charge pump current selection. Settling time will be approximately inversely proportional to the required HPF for the audio/data signal.

#### PLL Loop Filter

Faster PLL lock times are required in applications where time division duplexing or frequency hopping techniques is used. On the contrary, narrow band audio applications, which need low VCO phase noise, require tightening of PLL loop filter bandwidth. In the result, increases PLL lock time.

The loop filters employed are second order passive loop filters. Separate literatures are available for various filter response considerations and calculation of filter components. Dumping factor, phase noise and reference spurs are the main considerations beside lock time.

The following information is required for designing the PLL loop filter:

#### Kvco

0.1 - 1GHz Single Chip FM Transceiver

In 915MHz ISM band, when PLL voltage is about 1.8V, For RVCO, Kvco = 40MHz/V; For TVCO, Kvco = 23MHz/V.

Please note that at different PLL voltage or different operating frequency, the VCO gain may be different. In such situations, the VCO gains can be determined by measurement (VCO frequency change/PLL voltage change for 1 reference frequency step change).

#### **Charge Pump Current**

The available charge pump current settings are 0.2mA and 1.0mA for both Tx and Rx. The charge pump current is selected by programming the Mode register bits 6 (Rx) and 7 (Tx).

With proper consideration on damping factor, higher charge pump current reduces PLL lock time.

#### **Reference Frequency**

In general, larger reference frequency reduces PLL lock time. It is set by Reference Frequency Register.

### **RECEIVER ATTACK TIME**

#### Rx Baseband DC Offset Loop Response Time

Settling time is 2ms for an effective receiver baseband HPF of 100Hz. The HPF can be adjusted with changing the external capacitors on DCI/DCQ. Settling time will be approximately inversely proportional to the DCI/DCQ capacitors. When making such changes, consideration must be given to the required high pass filtering for the lowest possible frequency of the FM signal.

#### Auto Gain Control Response Time

Similar considerations apply as in RSSI Settling. Current recommendation is to set up the receiver to allow a gain change every 14ms for a receive bandwidth of 130kHz and every 56ms for a bandwidth of 16kHz. Note this only changes the gain by 1 step. For WE904, the gain is automatically set to maximum following the serial interface signal LE low so it could take 8x as long (110ms or 450ms) to get to minimum gain. For WE905, although this gain reset can be disable, time taken for gain to change from maximum to minimum is the same as WE904.

More information is available in section on Rx Gain Control.

0.1 - 1GHz Single Chip FM Transceiver

### FM MODULATION

### FM DEVIATION

The transmitter utilizes direct modulation method where the modulation signal is directly applied to the PLL loop filter.

FM deviation is depending on the a.c. voltage level of the applied modulation signal as well as TVCO gain. TVCO gain is in term, dependent on the TVCO frequency and TPLL voltage. It is normally desirable for FM deviation to be consistent for a given modulating voltage level.

For a circuit that is designed to operate at a Tx frequency band, the TVCO frequency is fixed by Transmit Frequency Register.

However, the locked TPLL voltage may differ from one unit to another. This is mainly due to the tolerance of external TVCO inductors and the choice of Tx trim bit which set the internal capacitance.

The solution is either to use tight tolerance TVCO inductors or a potential divider to adjust the voltage level of the modulating signal.

Using tight tolerance inductors, such as PCB printed inductors, FM deviation varies between board to board can be maintained within +/-20%. For more accurate FM deviation, a pot meter is required to adjust the modulating signal level.

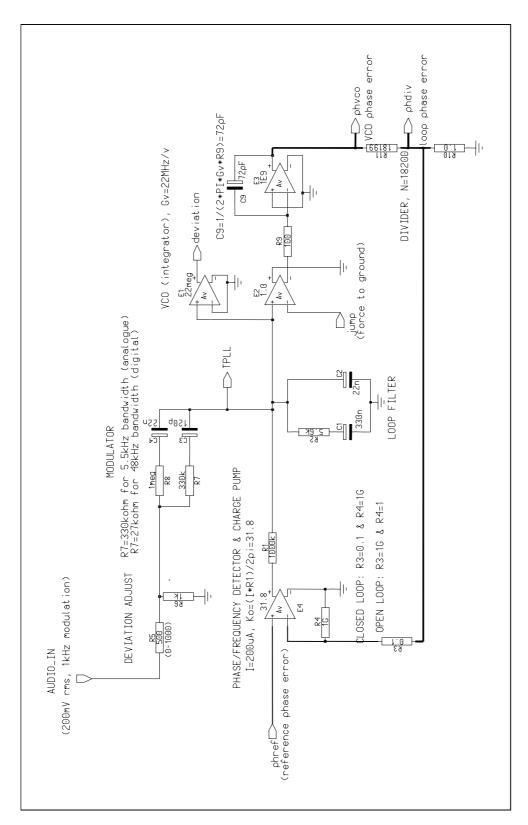

### FM MODULATOR

If there is a change in PLL loop filter, the Tx modulator components have to be changed to get the desired frequency response and Tx FM deviation.

Values for modulator components can be determined by simulation. How VCO frequency responses to an input to the modulator circuit (ac or transient) are simulated to obtain the correct modulator RC combination. Below is the circuit for modulator simulation.

0.1 - 1GHz Single Chip FM Transceiver

Model for Modulator / PLL Simulation

### AUTOMATIC FREQUENCY CONTROL (AFC)

In direct conversion, zero-IF receiver system, the frequency difference between receiving RF signal and the receiver LO produces a beat tone. If this beat tone falls in audio range, it will pass through the receiver filters and appear as an audible tone at audio output.

The Automatic Frequency Control (AFC) feature tunes the reference crystal oscillator to minimize frequency offset between receive RF signal and receive LO. The continuous tracking action keeps the Rx LO at a small distance (<100Hz) away from the Rx RF signal. As the beat tone frequency is now very low, the baseband DC offset correction circuit and external audio filter can easily reduce the beat tone to noise level.

The AFC pin 46 provides a DC correction signal corresponding to the amount of frequency offset. The signal changed the biasing, and hence the capacitance, of the varactor D1.

The RC network (C4, C5, C6, R5 and R6) and the decoupling capacitors (C7 and C8) at AFCC pin 47, determines the attack time of the AFC integration (double) loop. AFC response time is approximately 16ms.

Schematics of AFC circuit and relevant components

### **AFC CORRECTION RANGE**

The AFC correction range should be at least 2 x crystal frequency tolerance: including temperature, aging and tuning.

The steps to select components for the desire correction range are:

1. Determine C1, C2 and C3\*,

where C3\* is the equivalent capacitance of C3//TC1//D1.

The choice of C1, C2 and C3\* depends on the crystal load capacitance and drive level.

In figure above, the expected load capacitance of the 12.0MHz crystal is 18pF. The load capacitance presented by the circuit is approximately created by the series combination of C1, C2 and C3\*.

Choice of C1 and C2 are affected by the crystal drive level. E.G. for a load capacitance of 18pF:

| Drive level | 0.1uW | 0.1mW |

|-------------|-------|-------|

| C1, C2      | 82pF  | 47pF  |

| C3*         | 27pF  | 56pF  |

2. Determine the variation in  $C3^*$  ( $\Delta C3^*$ ) to provide correction range

This can be done experimentally by adjusting a trimmer capacitor or by calculation if the characteristics of the crystal are known.

3. Select varactor diode D1

Select a varactor that its change in capacitance from 2.5V to 0.1V is the slightly greater than  $\Delta C3^*$ .

The varactor use in the above AFC circuit has a capacitance of 10pF at 2.5V and 25pF at 0.1V. It gives an AFC correction range of +/- 20ppm.

4. Select trimmer TC1

Select trimmer cap TC1 to correct the initial tolerance of the crystal.

The trimmer capacitor in above AFC circuit varies from 4pF to 20pF and gives a tuning range of +/- 30ppm.

5. Select C3

If the mid value of D1 (~16pF) and TC1 (~9pF) is lesser than C3\*, then C3 (~2pF) is added to make up to the required C3\*.

### **SWITCHING AFC ON AND OFF DURING OPERATION**

When AFC is switched off, AFC output voltage will drop to 0V. The varactor capacitance will become maximum and pull the reference frequency to lowest point of the AFC correction range.

Therefore, if the application requires switching AFC off during operation, the resistor network R9 - R11 is required to provide a DC1.2V at the varactor. However, if AFC is always on during operation, this resistor network can be omitted.

### **CRYSTAL TUNING WITH AFC**

While tuning trimmer capacitor (TC1) to correct crystal error, it is necessary to fix the AFC voltage at mid value (1.2V)

This can be done by:

- 1. turning AFC off if the resistor network R9 R11 is in placed. Adjust TC1 until the Tx frequency is the same as the Tx Frequency Register.

- 2. connecting the Rx to a reference signal generator which is set to the receiving frequency of the Rx Frequency Register. Turn AFC on. Adjust TC1 until AFC voltage is about 1.2V.

### **WORKING CONDITIONS FOR AFC**

In a pair of transceivers, AFC is only required in one transceiver; although it is fine to have AFC on both transceivers.

In order for AFC to work properly, the receiving frequency must fall within the bandwidth of the receiver; and the frequency offset between receiving frequency and Rx LO must not be larger than what the AFC correction range can provide.

In data communication (FSK modulation) with low baud rate or without using non-return-to-zero technique, AFC may treat FSK deviation as frequency offset and "correct" it. In such situation, AFC should not be used.

### AFC NOISE

Although AFC removes the beat tone, it may result in another type of noise known as zero crossing pop noise. This noise may be audible in silent situation when there is no FM modulation in the receiving signal. This noise is removed by adding resistor R7 at AFCC.

Suitable value for R7 is between 560k $\Omega$  and 1M $\Omega$ .

#### AFC RESPONSE TIME

The series RC network connected from AFC pin to VSS, along with decoupling capacitors connected from AFCC pin 47 to VDD and VSS, determines the attack time of the AFC integration (double) loop.

With the component values shown in page 23, the AFC response time is approximately 16ms.

### SERIAL PROGRAMMING INTERFACE

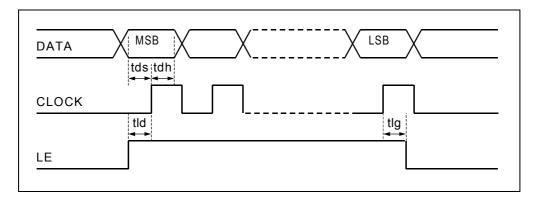

Tx/Rx frequencies, reference frequency, as well as various operational and test modes are controlled by a 3-wire serial bus comprised of Clock, Load Enable and Data. The programming word contains 23 bits. The first two bits (LSB) select the programming of the register for receive VCO frequency, transmit VCO frequency, reference frequency or device operational modes. The remaining bits contain the data to be programmed. The timing diagram below shows the relationship between Data, Clock, and Load Enable.

| LE                              |

|---------------------------------|

| DATA 23 22 21 20 19 6 5 4 3 2 1 |

Data is clocked into the internal shift registers on the positive edge of the CLOCK (pin 3), while Load Enable (pin 1) is held HIGH. Data is loaded from the shift registers into the data registers on the negative edge of the Load Enable (LE). This load is NOT synchronized with the programmable divider, i.e. the load is controlled directly by the negative falling edge of the Load Enable.

### TIMING DIAGRAM

- tds: Data set up time before +ve CLOCK edge 30ns min

- tdh: Data hold time after +ve CLOCK edge 30ns min

- tld: Latch Enable lead time before first +ve CLOCK edge. 30ns min

- tlg: Latch Enable lag time after last +ve CLOCK edge. 30ns min

0.1 - 1GHz Single Chip FM Transceiver

### **REFERENCE FREQUENCY REGISTER**

| Bit 1 (last bit lo<br>Bit 2 | aded)       | Load control bit 1 = (0)<br>Load control bit 2 = (0) |

|-----------------------------|-------------|------------------------------------------------------|

| Bit 3                       | Ref(1) LSB  | Reference divide register (count 1 to 2047)          |

| Bit 4                       | Ref(2)      | Reference divide register (count 1 to 2047)          |

| Bit 5                       | Ref(3)      | Reference divide register (count 1 to 2047)          |

| Bit 6                       | Ref(4)      | Reference divide register (count 1 to 2047)          |

| Bit 7                       | Ref(5)      | Reference divide register (count 1 to 2047)          |

| Bit 8                       | Ref(6)      | Reference divide register (count 1 to 2047)          |

| Bit 9                       | Ref(7)      | Reference divide register (count 1 to 2047)          |

| Bit 10                      | Ref(8)      | Reference divide register (count 1 to 2047)          |

| Bit 11                      | Ref(9)      | Reference divide register (count 1 to 2047)          |

| Bit 12                      | Ref(10)     | Reference divide register (count 1 to 2047)          |

| Bit 13                      | Ref(11) MSB | Reference divide register (count 1 to 2047)          |

| Bit 14                      | PDR(1)      | PDR select                                           |

| Bit 15                      | PDR(2)      | PDR select                                           |

| Bit 16                      | PDR(3)      | PDR select                                           |

|                             |             |                                                      |

| PDR (3) | PDR (2) | PDR (1) | Divide ratio, PDR |

|---------|---------|---------|-------------------|

| 0       | 0       | 0       | 2                 |

| 0       | 0       | 1       | 6                 |

| 0       | 1       | 0       | 12                |

| 0       | 1       | 1       | 24                |

| 1       | 0       | 0       | 36                |

| 1       | 0       | 1       | 48                |

| 1       | 1       | 0       | 72                |

| 1       | 1       | 1       | 96                |

Reference divide register (1 to 2047) sets the internal reference frequency.

#### Internal Reference Frequency = Reference Oscillator Frequency / Reference divide register

e.g. 12MHz reference crystal, Ref divider of 240, gives 50kHz internal reference frequency.

PDR select sets the IF and BWdm.

# FM Demodulator bandwidth,BWdm = (Receiver LO) / (580 x PDR)IF frequency,Fif = (Receiver LO) / (544 x PDR)

e.g. 915MHz frequency, PDR of 12, gives 131kHz demodulator bandwidth and 140kHz IF.

For the above example,

Programming word = 0000000 010 00011110000 00

### **RECEIVE FREQUENCY REGISTER**

| Bit 1 (last bit loa<br>Bit 2                                                                             | aded)                                                                                            | Load control bit 1 = (1)<br>Load control bit 2 = (0)                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 3 LSB<br>Bit 4<br>Bit 5 MSB                                                                          | Rf(1)<br>Rf(2)<br>Rf(3)                                                                          | Rx frequency F register<br>Rx frequency F register<br>Rx frequency F register                                                                                                                                                                                              |

| Bit 6 LSB<br>Bit 7<br>Bit 8<br>Bit 9<br>Bit 10 MSB                                                       | Ra(1)<br>Ra(2)<br>Ra(3)<br>Ra(4)<br>Ra(5)                                                        | Rx frequency A register<br>Rx frequency A register<br>Rx frequency A register<br>Rx frequency A register<br>Rx frequency A register                                                                                                                                        |

| Bit 11 LSB<br>Bit 12<br>Bit 13<br>Bit 14<br>Bit 15<br>Bit 16<br>Bit 17<br>Bit 18<br>Bit 19<br>Bit 20 MSB | Rm(1)<br>Rm(2)<br>Rm(3)<br>Rm(4)<br>Rm(5)<br>Rm(6)<br>Rm(6)<br>Rm(7)<br>Rm(8)<br>Rm(9)<br>Rm(10) | Rx frequency M register<br>Rx frequency M register |

| Bit 21<br>Bit 22<br>Bit 23                                                                               | Rx VCO Trim bit 1<br>Rx VCO Trim bit 2<br>Not Used                                               |                                                                                                                                                                                                                                                                            |

| Rx VCO | Trim Capacitor |               |

|--------|----------------|---------------|

| 2      | 1              |               |

| 0      | 0              | 0 – minimum C |

| 0      | 1              | 1             |

| 1      | 0              | 2             |

| 1      | 1              | 3 – maximum C |

#### Rx Frequency = Internal Reference Frequency x ((32 x M) + A + (F/8))

Trim capacitors are provided for correction of device tolerance.

e.g. 903.50625MHz RF, 50kHz reference frequency; div ratio 18070.125, assuming trim 2 Programming word = X10 1000110100 10110 001 01

### TRANSMIT FREQUENCY REGISTER

| Bit 1 (last bit lo<br>Bit 2                                                                              | baded)                                                                                  | Load control bit 1 = (0)<br>Load control bit 2 = (1)                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 3 LSB<br>Bit 4<br>Bit 5 MSB                                                                          | Tf(1)<br>Tf(2)<br>Tf(3)                                                                 | Tx frequency F register<br>Tx frequency F register<br>Tx frequency F register                                                                                                                                                                                                                         |

| Bit 6 LSB<br>Bit 7<br>Bit 8<br>Bit 9<br>Bit 10 MSB                                                       | Ta(1)<br>Ta(2)<br>Ta(3)<br>Ta(4)<br>Ta(5)                                               | Tx frequency A register<br>Tx frequency A register<br>Tx frequency A register<br>Tx frequency A register<br>Tx frequency A register                                                                                                                                                                   |

| Bit 11 LSB<br>Bit 12<br>Bit 13<br>Bit 14<br>Bit 15<br>Bit 16<br>Bit 17<br>Bit 18<br>Bit 19<br>Bit 20 MSB | Tm(1)<br>Tm(2)<br>Tm(3)<br>Tm(4)<br>Tm(5)<br>Tm(6)<br>Tm(7)<br>Tm(8)<br>Tm(9)<br>Tm(10) | Tx frequency M register<br>Tx frequency M register |

| Bit 21<br>Bit 22                                                                                         | Tx VCO Trim bit 1<br>Tx VCO Trim bit 2                                                  |                                                                                                                                                                                                                                                                                                       |

Bit 23 Tx VCO Trim bit 3

|   | Trim Capacitor |   |                |

|---|----------------|---|----------------|

| 3 | 2              | 1 | Thin Capacitor |

| 0 | 0              | 0 | 0 – Minimum C  |

| 0 | 0              | 1 | 1              |

| 0 | 1              | 0 | 2              |

| 0 | 1              | 1 | 3              |

| 1 | 0              | 0 | 4              |

| 1 | 0              | 1 | 5              |

| 1 | 1              | 0 | 6              |

| 1 | 1              | 1 | 7 – Maximum C  |

### Tx Frequency = Internal Reference Frequency x ((32 x M) + A + (F/8))

Trim capacitors are provided for correction of device tolerance.

e.g. 935.0625MHz RF, 50kHz reference frequency, div ratio 18701.25, assuming trim 2 Programming word = 010 1001001000 01101 010 10

0.1 - 1GHz Single Chip FM Transceiver

### **MODE REGISTER**

| Bit 1 (Last bit loaded)<br>Bit 2 |                                                                   |                     | Load control bi                            |                                         |

|----------------------------------|-------------------------------------------------------------------|---------------------|--------------------------------------------|-----------------------------------------|

| Bit 3<br>Bit 4<br>Bit 5<br>Bit 6 | AGC (Automatic Ga<br>Receiver<br>Transmitter<br>Receive Charge Pu | ,                   | 0 = Off<br>0 = Off<br>0 = Off<br>0 = 0.2mA | 1 = On<br>1 = On<br>1 = On<br>1 = 1.0mA |

| Bit 7                            | Transmit Charge P                                                 |                     | 0 = 0.2mA                                  | 1 = 1.0mA                               |

| Bit 8<br>Bit 9                   | Rx Charge Pump P<br>Tx Charge Pump P                              |                     | 0 = Normal<br>0 = Normal                   | 1 = Invert<br>1 = Invert                |

| Bit 10                           | Mixer Gain Control                                                |                     | (Bit 1)                                    |                                         |

| Bit 11                           | Mixer Gain Control                                                |                     | (Bit 2)                                    |                                         |

| Bit 12                           | Baseband Gain & F                                                 |                     | (Bit 1)                                    |                                         |

| Bit 13                           | Baseband Gain & F                                                 | RF Pad Control      | (Bit 2)                                    |                                         |

| Bit 14                           | Baseband Gain & F                                                 | RF Pad Control      | (Bit 3)                                    |                                         |

| Bit 15                           | For WE904 AFC Po                                                  | olarity             | 0 = Normal                                 | 1 = Invert                              |

|                                  | For WE905 AGC G                                                   | ain Reset           | 0 = Reset                                  | 1 = No Reset                            |

| Bit 16                           | AFC Enable                                                        |                     | 0 = Disable                                | 1 = Enable                              |

| Bit 17                           | Audio/Data Output                                                 | Select              | 0 = Analog                                 | 1 = Digital                             |

| Bit 18                           | Mode (Bit 1)                                                      | 0 for Normal mode.  | See page 33 &                              | 34 for other modes                      |

| Bit 19                           | Mode (Bit 2)                                                      | 0 for Normal mode.  | See page 33 &                              | 34 for other modes                      |

| Bit 20                           | Mode (Bit 3)                                                      | 0 for Normal mode.  | See page 33 &                              | 34 for other modes                      |

| Bit 21                           | Mode (Bit 4)                                                      | [Tse_0] in Normal N | Mode. See page                             | 33 & 34 for other modes                 |

| Bit 22                           | Mode (Bit 5)                                                      | [Tse_1] in Normal N | Node. See page                             | 33 & 34 for other modes                 |

### RX GAIN CONTROL (BIT 3, 10-15, 18-19)

The receiver section includes a facility to switch overall gain to maintain linearity over a wide dynamic range of on-channel signal levels. This can be done manually or automatically via an on-chip automatic gain control (AGC) circuit.

#### Automatic Mode (Bit 3 = 1; AGC ON)

When this bit is set to 1, the receiver will set the internal gain stages according to the received signal as shown in the following table.

| Nominal RF |            | Attenuation dB from maximum gain |          |                       |                       |                       |                       |

|------------|------------|----------------------------------|----------|-----------------------|-----------------------|-----------------------|-----------------------|

| Signal     | Level      | RF section                       |          | Baseband section      |                       |                       |                       |

| Increasing | Decreasing | RF Pad                           | RF Mixer | 1 <sup>st</sup> Block | 2 <sup>nd</sup> Block | 3 <sup>rd</sup> Block | 4 <sup>th</sup> Block |

|            | < -92dBm   | 0                                | 0        | 0                     | 0                     | 0                     | 0                     |

| > -86dBm   | < -82dBm   | 0                                | 0        | 0                     | 10                    | 0                     | 0                     |

| > -76dBm   | < -72dBm   | 0                                | 0        | 0                     | 10                    | 10                    | 0                     |

| > -66dBm   | < -62dBm   | 0                                | 10       | 0                     | 10                    | 10                    | 0                     |

| > -56dBm   | < -52dBm   | 0                                | 10       | 10                    | 10                    | 10                    | 0                     |

| > -46dBm   | < -42dBm   | 0                                | 20       | 10                    | 10                    | 10                    | 0                     |

| > -36dBm   | < -32dBm   | 0                                | 20       | 10                    | 10                    | 10                    | 10                    |

| > -26dBm   | < -22dBm   | 10                               | 20       | 10                    | 10                    | 10                    | 10                    |

| >-16dBm    |            | 10                               | 30       | 10                    | 10                    | 10                    | 10                    |

In this mode, the mixer gain and baseband gain settings (bit 10-14) are ignored.

#### Manual Mode (Bit 3 = 0; AGC OFF)

In this mode, receiver gain stages are manually controlled by programming the Mode register bit 10 to 14.

#### **RF Mixer Attenuation Control Table**

| Mode Re | gister Bit | RF Mixer        |

|---------|------------|-----------------|

| 11      | 10         | Attenuation, dB |

| 0       | 0          | 30              |

| 0       | 1          | 20              |

| 1       | 0          | 10              |

| 1       | 1          | 0               |

#### Baseband Gain and RF Pad Control Table

| Mod | e Registe | r Bit | Baseband Stage Attenuation, dB |                       |                       | RF Pad Attn,          |    |

|-----|-----------|-------|--------------------------------|-----------------------|-----------------------|-----------------------|----|

| 14  | 13        | 12    | 1 <sup>st</sup> Block          | 2 <sup>nd</sup> Block | 3 <sup>rd</sup> Block | 4 <sup>th</sup> Block | dB |

| 0   | 0         | 0     | 10                             | 10                    | 10                    | 10                    | 10 |

| 0   | 0         | 1     | 10                             | 10                    | 10                    | 10                    | 0  |

| 0   | 1         | 0     | 10                             | 10                    | 10                    | 0                     | 0  |

| 0   | 1         | 1     | 0                              | 10                    | 10                    | 0                     | 0  |

| 1   | 0         | 0     | 0                              | 10                    | 0                     | 0                     | 0  |

| 1   | 0         | 1     | 0                              | 0                     | 0                     | 0                     | 0  |

### Tse Signal Evaluation Time (Bit 21 & 22)

Applicable only if AGC is ON, bit 3 = 1.

To determine the correct gain setting for AGC, the received on-channel signal is integrated in the baseband section. The integrated signal level is evaluated at regular time intervals: signal evaluation time Tse. Tse is programmed by bits 21 & 22 of the Mode Register. The available Tse values are inversely proportional to the demodulator bandwidth, BWdm, allowing for the signal evaluation over a similar number of baseband cycles of an on-channel signal.

Recommendations for setting Tsi and Tse are as follow:

Recommended value for Tsi is:

#### Tsi = 0.9ms x (130kHz/BWdm) + 1.6ms + 4.5ms x (65kHz/BWbb)

where BWdm is the demodulator bandwidth and BWbb is the base band bandwidth

Recommended value for Capacitance at GCC pin is:

The recommended capacitance CGCC attached to GCC pin, for a given signal integration time constant, Tsi, is

#### CGCC = 330nF x (Tsi / 27ms)

Recommended value for Tse is:

Tse > 2 x Tsi

Possible values for Tse are:

| Tse_1 | Tse_0 | Period               |

|-------|-------|----------------------|

| 0     | 0     | 7ms x (130kHz/BWdm)  |

| 0     | 1     | 14ms x (130kHz/BWdm) |

| 1     | 0     | 28ms x (130kHz/BWdm) |

| 1     | 1     | 56ms x (130kHz/BWdm) |

- e.g. 1 For 65kHz BWbb, 130kHz BWdm Recommended Tsi = 7ms, CGCC = 85.6nF, Tse ≥ 14ms Choose CGCC = 82nF, then Tsi = 6.7ms Choose Tse bits = 01 which gives Tse=14ms Change from maximum to minimum gain takes 110ms.

- e.g. 2 For 16kHz BWbb, 32kHz BWdm Recommended Tsi = 24ms, CGCC = 293nF, Tse ≥ 48ms Choose CGCC = 300nF , then Tsi = 24.5ms Choose Tse bits = 01 which gives Tse=57ms Change from maximum to minimum gain takes 456ms.

### AGC GAIN RESET DISABLE (BIT 15, WE905 ONLY)

In WE904, when AGC is on, any change made to any register will reset the gain to maximum automatically. The gain then switches automatically according to the measured signal level.

In WE905, bit 15 of the Mode Register offers a choice to disable the gain reset. If bit 15 is set to 1 and a register is being programmed, the gain setting will remain the same before and after the programming.

### AFC POLARITY (BIT 15, WE904 ONLY)

For the AFC application circuit shown in AFC section, the AFC polarity is Normal. However, if the varactor diode is connected such that its anode is connected to AFC signal and cathode is connected to supply, then AFC polarity should be inverted.

### **CHARGE PUMP CURRENT AND POLARITY (BIT 6-9)**

Available charge pump current for Tx and Rx VCOs are 0.2mA and 1mA. With proper choice of PLL loop filter components, higher charge pump current provides faster lock time. Please refer to section on Rx/Tx PLL Lock Time for more information.

For the application circuit shown in page 3, the PLL lock time is optimized for Rx charge pump current of 1.0mA and Tx charge pump current of 0.2mA.

Charge pump polarity is always Normal except if external VCO circuit is used. If the tuning diode's anode is connected to ground and the PLL voltage is connected to the cathode, then the charge pump polarity must be inverted.

### ANALOG VS DIGITAL OUTPUT (BIT 17)

The receiver AFO output can be configured to either analog or digital mode.

In the Digital Mode, the demodulated signal goes through an internal data slicer before being output as CMOS compatible logic data.

Polarity of RX data is the same as received FM deviation, i.e. no data inversion. A positive FM deviation produces a 1 and a negative FM deviation produces a 0. However, please note that due to the design of TX VCO, a 1 in the TX data produces a negative FM deviation and a 0 produces a positive FM deviation. Hence, when two WE2408 are used as data communication pair, the RX data will be inverted compare to the TX data.

In the Analog Mode, the output pin provides the recovered, demodulated audio signal without passing through the data slicer.

Polarity of RX waveform is the opposite of the received FM deviation, i.e. signal inversion. A positive FM deviation produces a lower voltage and a negative FM deviation produces a higher voltage. Since, TX FM modulation is inverted, when two WE2408 are used as analog communication pair, the RX signal will look the same as the TX signal, i.e. no inversion.

### **OPERATION MODES (BIT 18-22)**

In Normal Mode, the AFO output can be configured to either analog or digital mode. In the Analog Mode, this output pin provides the recovered, demodulated audio signal. In the Digital Mode, the demodulated signal goes through an internal data slicer before being output as CMOS compatible logic data.

Other than Normal Mode, the device offers test modes (in both WE904 and WE905) and 2 other special operating modes in WE905. In Test Mode, The AFO output pin can be configured to provide signal at various stages in the receiver path for trouble-shooting purpose.

The special operating modes available on WE905 are Tx Charge Pump Disable Mode and Reference Oscillator On Mode

#### **Other Modes for WE904**